# Silicon Tunnel FETs for digital and analogue applications

von der Fakultät für Elektrotechnik und Informationstechnik der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Ingenieurwissenschaften genehmigte Dissertation

vorgelegt von

M.Sc. Keyvan Narimani

aus

#### Kangavar

Berichter: Univ.-Prof. Dr. rer. nat. Joachim Knoch Apl.Prof.Dr.phil. Siegfried Mantl

Tag der mündlichen Prüfung: 11. Dezember 2018

Diese Dissertation ist auf den Internetseiten der Universitätsbibliothek online verfügbar

# Kurzfassung

Aufgrund der steigenden Zahl von Transistoren pro Einheitsfläche in integrierten Schaltungen erlangt die Verlustleistung zunehmende Bedeutung. Die Verringerung der Versorgungsspanung VDD ist eine wichtige Maßnahme die dynamische und statische Leistungsaufnahme zu reduzieren. Aufgrund der inhärenten physikalischen Begrenzungen eines Metal-Oxide-Halbleiter-Feldeffekttransistors (MOSFET), führt dies zu entweder einem reduzierten An-Strom Ion oder erhöhtem Aus-Strom Ioff. Der Tunnel-Feldeffekttransistor (TFET) hingegen ist ein vielversprechendes Bauelement, welches erlaubt diese Begrenzungen zu überschreiten. Dies ist möglich, da der TFET auf quantenmechanischen Band-zu-Band Tunneln als Hauptladungstransport beruht, im Vergleich zur thermischen Emission bei MOSFETs.

In dieser Arbeit werden zwei verschiedene Vorschläge eines TFET-Konzeptes diskutiert, die auf Punkt- und Linien-Tunneln basieren. Beide Konzepte sind jeweils hinsichtlich Band-zu-Band Tunnelns optimiert, auf Basis physikalischer Modelle, welche sich aus der WKB-Näherung ergeben. Die Optimierung diente dem Ziel, einen höheren An-Strom und bessere inverse Unterschwellensteigung SS (<60 mV/dec) zu ermöglichen. Die auf Punkt-Tunneln basierenden TFETs verwenden einen einzelnen Nanodraht (NW), der auf verspannten Silizium-auf-Isolator (sSOI) prozessiert wird. Der Nanodraht ist rundherum von einem High-k/Metal-Gate umgeben, um die elektrostatische Kontrolle des Kanals zu optimieren. Ionenimplantation und Aktivierung von Dotierstoffen wurden sorgfältig angepasst, um die Qualität des Tunnelkontaktes Schritt für Schritt zu verbessern. Der optimierte TFET zeigt verbesserten An-Strom Ion, Ion/Ioff Verhältnis sowie sehr gutes mittlere SSavg. Zusätzlich werden verschiedene Analog-Eigenschaften der Nanodraht TFETs präsentiert. Tieftemperaturmessungen ermöglichen eine Verschlechterung der Leistung von NW-TFETs bei kleinen Gatespannungen nachzuweisen, welche Tunneln über Störstellen (TAT) entstammt

Um ungewolltes ambipolares Verhalten zu verhindern, welches in jedem TFET inhärent auftritt, wird ein TFET mit einem SiO2 Abstandhalter im Drain-Gate Zwischenraum vorgestellt. Dies unterdrückt effektiv den Tunnelkontakt auf der Drain-Seite. Als Folge wird das ambipolare Schaltverhalten vollkommen unterdrückt, wodurch die Eignung der TFETs sowohl im Bereich digitaler als auch analoger Anwendungen gezeigt wird.

Als zweites Konzept wird ein planarer Si TFET hergestellt, der auf Linien-Tunneln basiert, welches bessere Unterschwell-Eigenschaften ermöglicht. Nach Ionenimplantation und Aktivieren der Dotierstoffe wird der Source-Schicht verdünnt, so dass Implantationsschäden entfernt werden. Die so gefertigten Bauelemente zeigen sehr deutlich verbesserte SS von 55 mV/dec über zwei Dekaden des elektrischen Source-Drain-Stroms.

Inverter Schaltungen aus komplementären NW-TFETs (CTFETs), sowohl mit als auch ohne ambipolare Eigenschaften, wurden hergestellt und verglichen. Es konnte gezeigt werden, dass die Unterdrückung des ambipolaren Verhaltens den Rauschpegel positiv beeinflusst.

Eine hohe Temperaturstabilität von Stromspiegeln wird diskutiert, welche auf zwei NW-TFETs basieren. Die Messungen zeigen stabilen Betrieb der Schaltung auch bei hohen Temperaturen, wenn die Transistoren BTBT-Bereich arbeiten.

# Abstract

As number of transistors per unit area in integrated circuits increases, power dissipation of the chips becomes progressively important. Scaling of supply voltage VDD is an important measure to decrease dynamic Pdynamic and static Pstatic power consumption of integrated circuits. However, considering inherent limitation of MOSFETs, this either leads to low operating current or increased leakage current. The tunnel field effect transistor (TFET) is a promising alternative to go beyond this limitation to operate devices at very small supply voltage VDD due to non-thermal quantum mechanical band to band tunneling as the main carrier transport mechanism compared to thermal emission in MOSFETs.

In this work, two different TFET design concepts based on point-tunneling and line-tunneling are investigated. In each case, the tunneling probability is optimized with regard to basic physical relations derived from the WKB approximation of band to band tunneling. The end goals are to achieve higher drive currents at lower supply voltages and subthermal (<60 mV/dec) inverse subthreshold swings. The point-tunneling based devices are fabricated as single nanowire gate-all-around TFETs based on tensile-strained silicon on insulator(sSOI) wafers. The devices are highly scaled and employ high-k HfO2 gate dielectric to achieve optimum electrostatic control over the channel. Moreover, careful adjustments of ion implantation and dopant activation in various settings ensure favorable tunneling junction formation. The optimized device shows superior on-current Ion, Ion/Ioff ratio as well very good average subthreshold swing SSavg. For this device, various analog figures of merits are also presented. Low temperature measurements reveal insights about the limiting effect of trap-assisted-tunneling(TAT) at low gate voltages on performance of the fabricated nanowire TFETs.

Parasitic ambipolar behavior which is inherent to TFET operation is suppressed by employing a SiO2 spacer to form a gate-drain underlap, effectively switching off the drain tunneling junction. As a result, the ambipolar behavior of NW TFETs fabricated by this method is completely suppressed, making them suitable for different digital and analog circuit applications.

To achieve enhanced subthreshold characteristics, line-tunneling based planar silicon TFETs are designed and fabricated by thinning down the source after implantation and dopant activation to get rid of the end of the range (EOR) damage. Devices

fabricated by this method show superior SS of 55 mV/dec over two decades of drain current.

Complementary single NW TFET inverters with and without ambipolarity are fabricated and compared. It is revealed that the suppression of ambipolarity has a positive effect on noise margin of inverters, where the logic levels match the actual bias points.

High temperature stability of two-transistor current mirrors based on nanowire TFETs is also evaluated. The measurements show stable operation of the circuit even at high temperatures when the transistors operate in the BTBT region.

# Contents

| 1        | Intr                        | roduction                                                  | 1  |

|----------|-----------------------------|------------------------------------------------------------|----|

| <b>2</b> | $\operatorname{Th}\epsilon$ | eoretical Background                                       | 5  |

|          | 2.1                         | Limitations of power scaling in ICs                        | 5  |

|          | 2.2                         | MOSFET operation                                           | 6  |

|          | 2.3                         | Tunnel FET operation                                       | 8  |

|          |                             | 2.3.1 BTBT model                                           | 9  |

|          |                             | 2.3.2 TFET subthreshold behavior                           | 10 |

|          |                             | 2.3.3 Point tunneling vs line tunneling                    | 12 |

|          | 2.4                         | TFET design factors                                        | 13 |

|          |                             | 2.4.1 Electrostatic control                                | 13 |

|          |                             | 2.4.2 Doping profile                                       | 16 |

|          | 2.5                         | TFET non-ideal processes                                   | 17 |

|          |                             | 2.5.1 Trap assisted recombination                          | 17 |

|          |                             | 2.5.2 Trap assisted tunneling(TAT)                         | 19 |

|          |                             | 2.5.3 Super-linear onset                                   | 20 |

|          |                             | 2.5.4 Ambipolar behavior                                   | 21 |

| 3        | $\mathbf{G}\mathbf{A}$      | A Single NW Silicon TFETs, experiment and simulation       | 23 |

|          | 3.1                         | Introduction                                               | 23 |

|          | 3.2                         | Device Fabrication                                         | 23 |

|          | 3.3                         | Variability in TFETs                                       | 28 |

|          |                             | 3.3.1 Method of simulation                                 | 29 |

|          |                             | 3.3.2 Comparison of experimental and simulation results    | 30 |

|          | 3.4                         | Electrical characterization of GAA Single NW Silicon TFETs | 33 |

|          |                             | 3.4.1 DC Characteristics                                   | 33 |

|          | 3.5                         | Effect of trap assisted tunneling                          | 41 |

|          |                             | 3.5.1 Density of interface traps                           | 43 |

## CONTENTS

| $_{ m Li}$       | $\mathbf{st}$ of | Publications                              | Ι         |

|------------------|------------------|-------------------------------------------|-----------|

| $\mathbf{R}_{0}$ | efere:           | ices                                      | 99        |

| 7                | Con              | clusion and outlook                       | 95        |

|                  | 6.2              | Conclusion                                | 92        |

|                  |                  | •                                         | 89        |

|                  |                  |                                           | 87        |

|                  | 6.1              |                                           | 86        |

| 6                | TFI              |                                           | <b>85</b> |

|                  | 5.6              | Conclusion                                | 84        |

|                  | 5.5              |                                           | 81        |

|                  | 5.4              |                                           | 78        |

|                  | 5.3              |                                           | 76        |

|                  | 5.2              |                                           | 72        |

|                  | 5.1              |                                           | 70        |

| 5                |                  | 3                                         | 69        |

|                  | 4.4              | Concrusion                                | 07        |

|                  | 4.3<br>4.4       |                                           | 67        |

|                  | 4.9              | 1                                         | 62<br>64  |

|                  |                  | 1                                         | 61        |

|                  |                  |                                           | 60        |

|                  | 4.2              | 0                                         | 59        |

|                  |                  | ( /                                       | 56        |

|                  | 4.1              |                                           | 55        |

| 4                |                  |                                           | 55        |

|                  | 3.7              | Conclusion                                | 54        |

|                  | 3.6              | 1                                         | 50        |

|                  |                  | 3.5.3 Energy level of traps               | 49        |

|                  |                  | 3.5.2 Low Temperature I-V characteristics | 47        |

|                  |                  |                                           |           |

# List of Figures

| 2.1 | (a) Scaling down $V_{DD}$ . In comparison the characteristics of a TFET is      |    |

|-----|---------------------------------------------------------------------------------|----|

|     | also depicted (b) Decreasing $V_{th}$ to reach desired on current at a lower    |    |

|     | $V_{DD}$ , resulting in high $I_{off}$                                          | 6  |

| 2.2 | Schematic illustration of an n-MOSFET and its energy band diagram.              |    |

|     | By increasing the applied gate voltage $V_{gs}$ , potential barrier height for  |    |

|     | electrons decreases allowing thermionic transport from the source to            |    |

|     | drain                                                                           | 7  |

| 2.3 | Schematic illustration of a TFET structure. It is a gated pin diode             |    |

|     | which is reversely biased through the gate on top of the gate oxide             | 9  |

| 2.4 | Illustration of TFET band structure when biased as a p-TFET. By                 |    |

|     | increasing the absolute value of gate voltage $V_g$ the channel bands           |    |

|     | move up until an energy overlap for BTBT between channel valance                |    |

|     | band and source conduction band appear                                          | 10 |

| 2.5 | BTBT barrier in 1D is approximated by a rectangular shape                       | 11 |

| 2.6 | Schematic illustration of point and line tunneling processes. Point             |    |

|     | tunneling(violet arrows) is confined to a small area directly under the         |    |

|     | gate while line tunneling(white arrows) takes place along the gate-             |    |

|     | source overlap perpendicular to the gate. In a real device both of              |    |

|     | these tunneling mechanisms are more or less present                             | 12 |

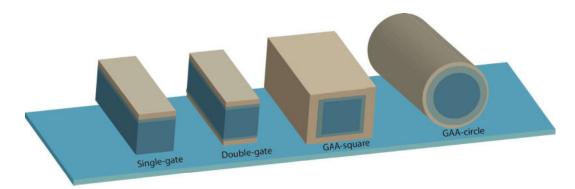

| 2.7 | Schematics of different single and multi-gate structures. As number of          |    |

|     | gates increases, the complexity of fabrication also increases                   | 14 |

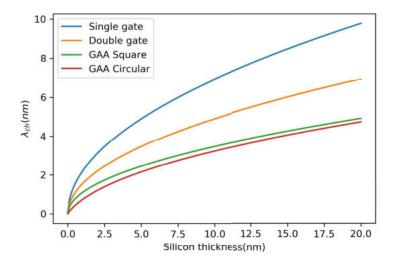

| 2.8 | Calculation of screening length $\lambda_{ch}$ for single and multi-gate device |    |

|     | structures. The circular GAA structure achieves the best(the mini-              |    |

|     | mum) value of the parameter                                                     | 14 |

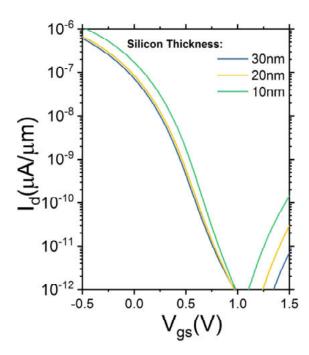

| 2.9 | Simulated transfer characteristics of double gate TFETs for different           |    |

|     | Si thicknesses. $I_{on}$ and average SS improve by decreasing the layer         |    |

|     | body-thickness.                                                                 | 15 |

# LIST OF FIGURES

| 2.10    | Illustration of trap assisted recombination within the bandgap of a TFET at off-state                                                                                                                                     | 17       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.11    | Schematics of trap assisted tunneling(TAT) process. Carriers tunneling into the available traps states at source/channel interface before being thermionically excited into the channel                                   | 19       |

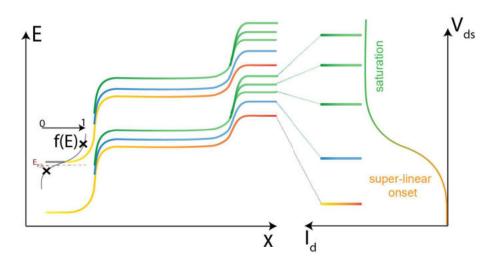

| 2.12    | Schematic illustration of super-linear onset in a TFET output characteristics at sufficiently large gate voltage $V_{gs}$                                                                                                 | 20       |

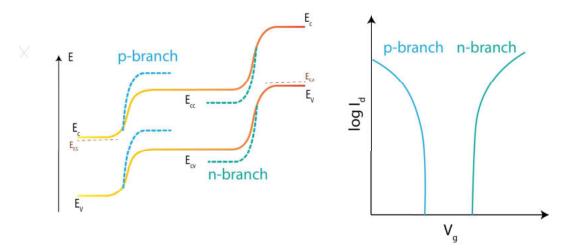

| 2.13    | Schematic illustration of ambipolar behavior in a TFET                                                                                                                                                                    | 21       |

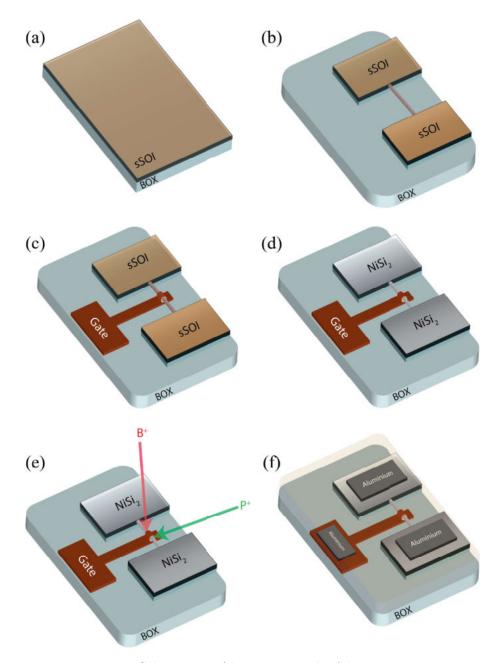

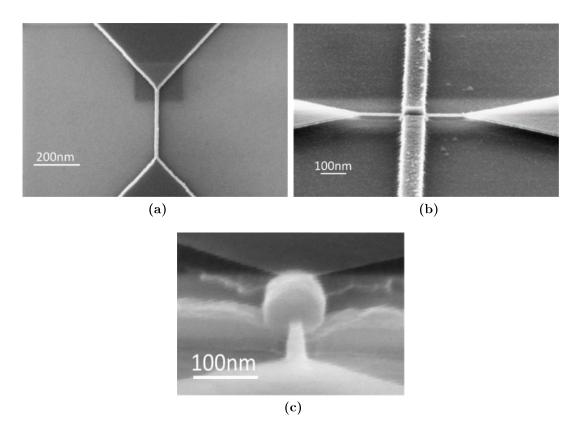

| 3.1 3.2 | Schematics of key steps in the fabrication process                                                                                                                                                                        | 25       |

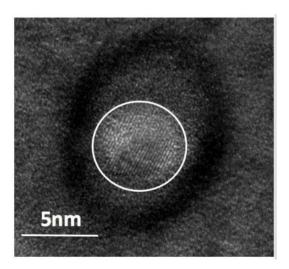

| 3.3     | (c) Side view of the nanowire TFET after silicidation and implantation.  Cross-section TEM image of a NW TFET                                                                                                             | 26<br>28 |

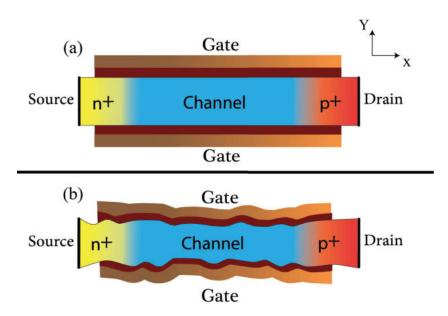

| 3.4     | (a)Nominal structure generated by Sentaurus TCAD (b) Generated structure with random line edge roughness. In total 80 random structures were generated. Since the structure is simulated as p-TFET, n <sup>+</sup>        | 20       |

|         | is chosen as source.                                                                                                                                                                                                      | 29       |

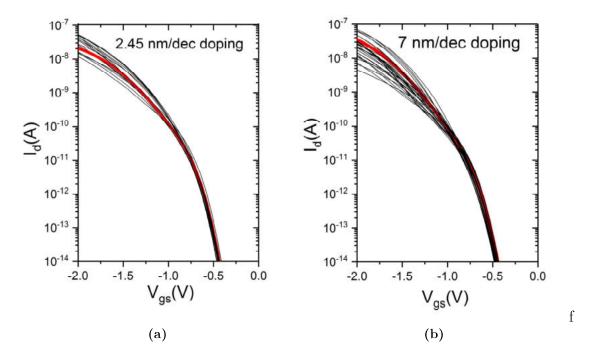

| 3.5     | Simulated transfer characteristics for devices with line edge roughness for a doping steepness of: (a) 2.45nm/dec, (b) 7nm/dec. The nominal curve is marked in red for each case                                          | 30       |

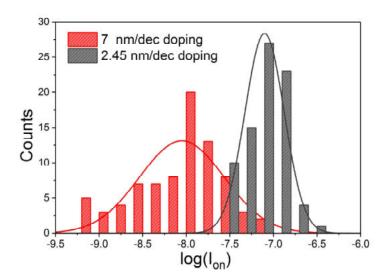

| 3.6     | Histogram of simulated $I_{on}$ distribution for two different doping profile. The table summarizes the normal distribution parameters mean,                                                                              |          |

|         | standard deviation and coefficient of variation                                                                                                                                                                           | 31       |

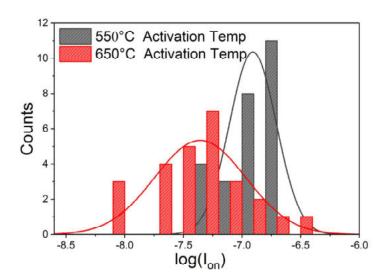

| 3.7     | Histogram of experimental $I_{on}$ distribution for two different activation temperatures 550°C and 650°C. The table summarizes the normal distribution parameters mean, standard deviation and coefficient of variation. | 32       |

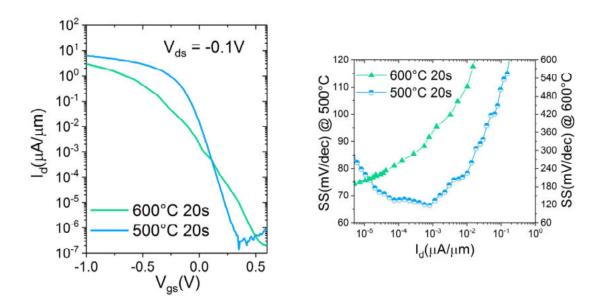

| 3.8     | (a) Measured transfer characteristics $I_d - V_{gs}$ and (b) SS versus $I_d$ plots                                                                                                                                        | 92       |

|         | for Set1                                                                                                                                                                                                                  | 35       |

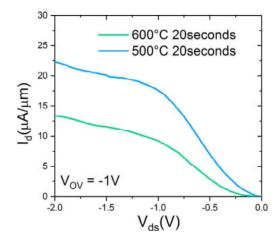

| 3.9     | Measured output characteristics of Set1 transistors for two different activation temperature at 500°C (blue) and 600°C (green)                                                                                            | 35       |

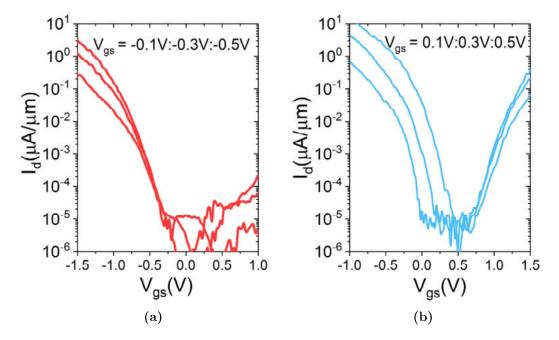

| 3.10 | Measured transfer characteristics $I_d$ - $V_{gs}$ of Set2 devices for (a) p-TFET and (b) n-TFET                                                                                                                                                                                                 | 36 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

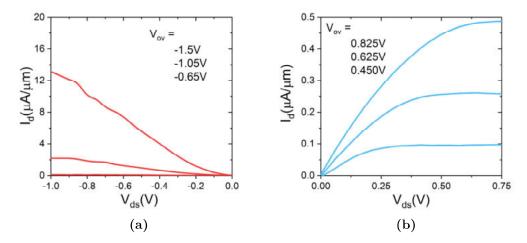

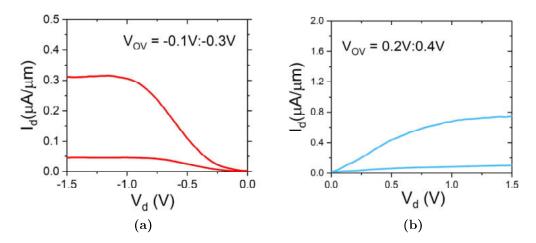

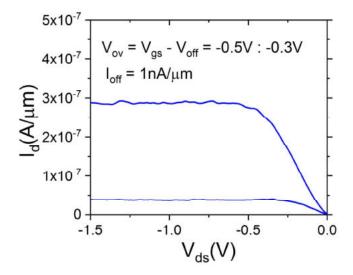

| 3.11 | Measured output characteristics $I_d$ - $V_{ds}$ of Set2 devices for (a) p-TFET and (b) n-TFET                                                                                                                                                                                                   | 37 |

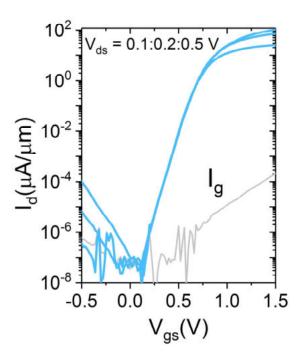

| 3.12 | Measured transfer characteristics $I_d$ - $V_{gs}$ of Set3 n-TFET. The gate leakage $I_g$ is shown in gray color                                                                                                                                                                                 | 38 |

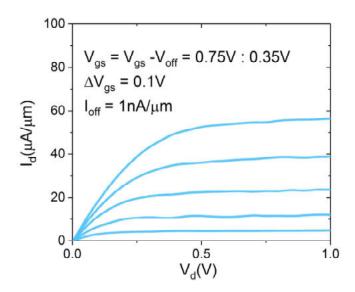

| 3.13 | Measured output characteristics of transistor Set3 n-TFET for different values of $V_{ov}$ . The device shows very go od $I_{on}$ of $15\mu\text{A}/\mu\text{m}$ at $V_{dd}=0.5V$ and very good saturation                                                                                       | 39 |

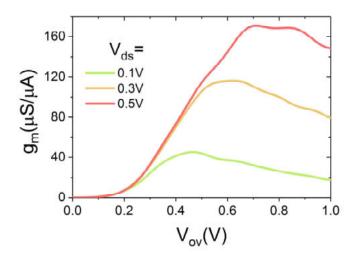

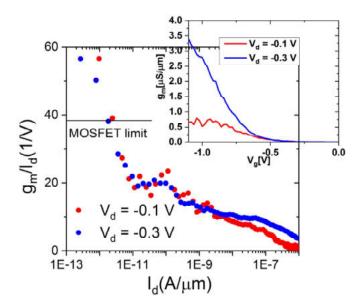

| 3.14 | Extracted transconductance $g_m$ for the sSi single NW GAA n-TFET shown in Figure 3.12 different $V_{ds}$ values                                                                                                                                                                                 | 40 |

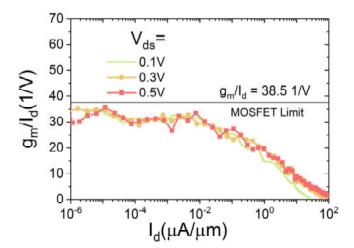

| 3.15 | Extracted transconductance efficiency $g_m/I_d$ for sSi single NW GAA n-TFET shown in Figure 3.12 as a function of drain current $I_d$ for different $V_{ds}$ values                                                                                                                             | 40 |

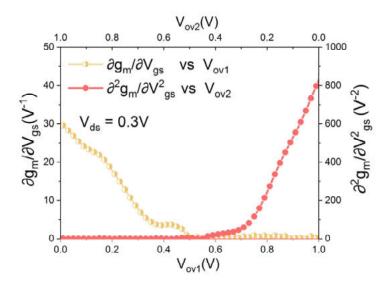

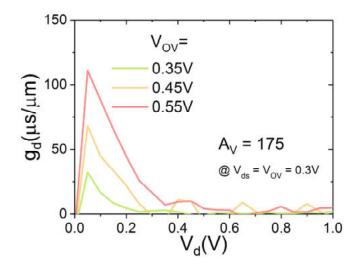

| 3.16 | Calculated $\frac{\partial g_m}{\partial V_{gs}}$ and $\frac{\partial^2 g_m}{\partial V_{gs}^2}$ terms for the sSi single NW GAA n-TFET shown in Figure 3.12. Both terms drop to small values indicating good higher order linearity of $I_d$ , particularly important for analog circuit design | 42 |

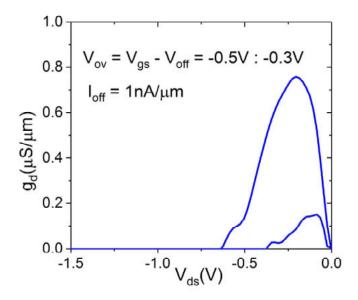

| 3.17 | Calculated output conductance $g_d$ for the sSi single NW GAA n-TFET shown in Figure 3.12 dropping to small values revealing good current saturation. A high voltage gain, $A_V = 175$ at about $V_{ov} = 0.3$ V is obtained                                                                     | 42 |

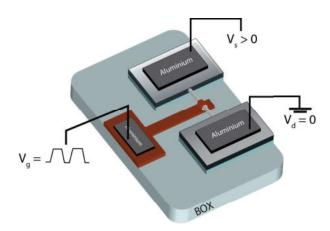

| 3.18 | Schematics of charge pumping measurement setup for a NW TFET. The source contact is reverse biased while keeping the drain at zero volt. Trapezoidal voltage pulse is applied to the gate, by varying $V_{base}$ changing the device condition between accumulation and inversion.               | 44 |

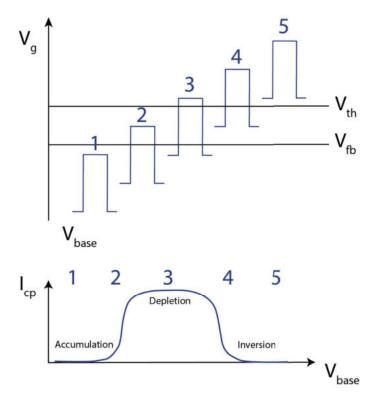

| 3.19 | Various zones when sweeping $V_{base}$ in charge pumping measurement.<br>As the base crosses $V_{fb}$ and $V_{th}$ , it gives rise to 5 different operation zones marked by numbers 1-5 in the plot                                                                                              | 45 |

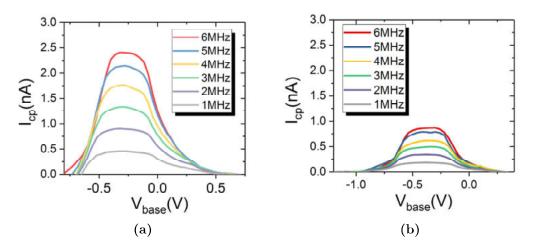

| 3.20 | $I_{cp}$ current versus $V_{base}$ for (a) before FG annealing (b) after FG annealing                                                                                                                                                                                                            | 46 |

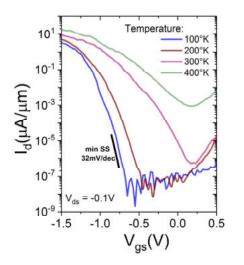

| ა.    | 21 Transfer characteristics of silicon GAA single NW p-TFET with NW dimension of 35nmx10nm and gate length of 350nm measured for tem-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | peratures ranging from 400°K to 100°K)(b) Measured minimum SS of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|       | the p-TFET as a function of T temperature. The theoretical limit of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.0      |

|       | SS for MOSFETs is also shown for comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48       |

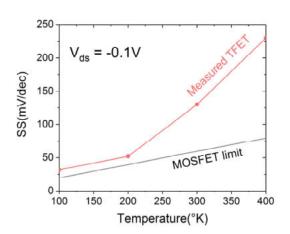

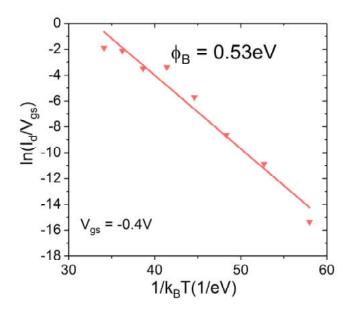

| 3.    | 22 Activation energy plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49       |

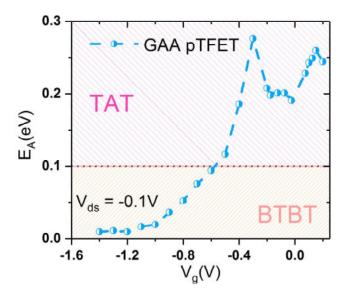

| 3.    | 23 Extracted barrier height $\phi_B$ for thermal excitations from trap states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50       |

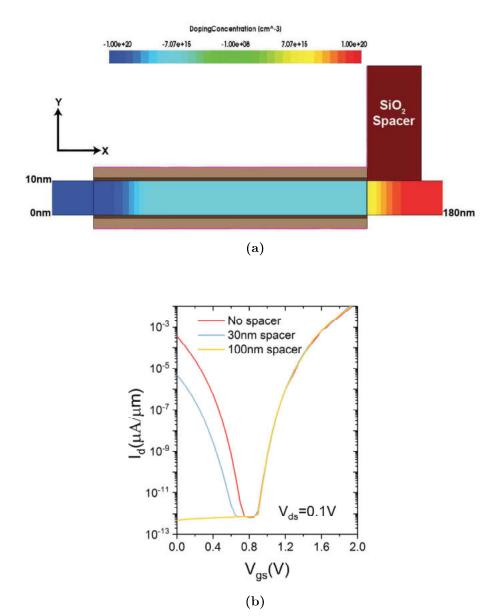

| 3.    | 24 (a) 2D simulation structure of nTFET with drain-gate underlap cre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|       | ated via $SiO_2$ deposition on the drain side. (b) Effect of drain-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|       | underlap length on the ambipolar branch of the simulated nTFET. $$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51       |

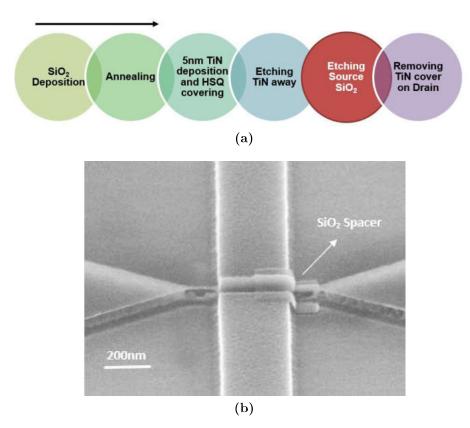

| 3.    | 25 (a) Fabrication steps of the gate-drain underlap. (b) Side view SEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|       | image of a NW with gate-drain underlap fabricated with a $\mathrm{SiO}_2$ spacer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52       |

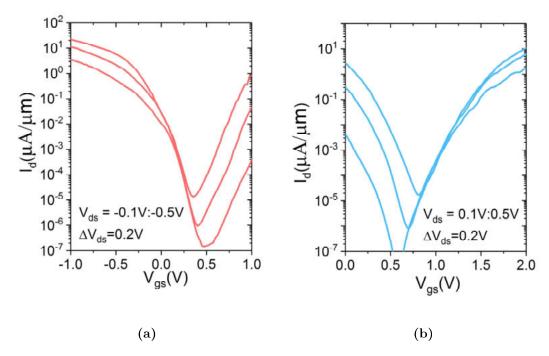

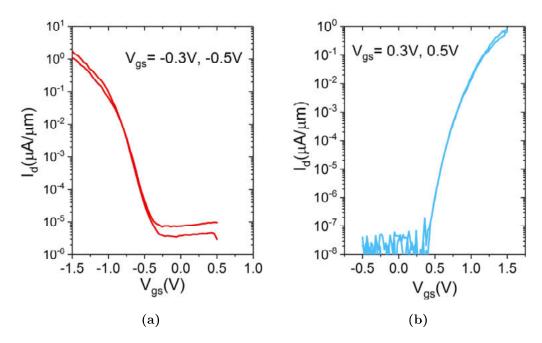

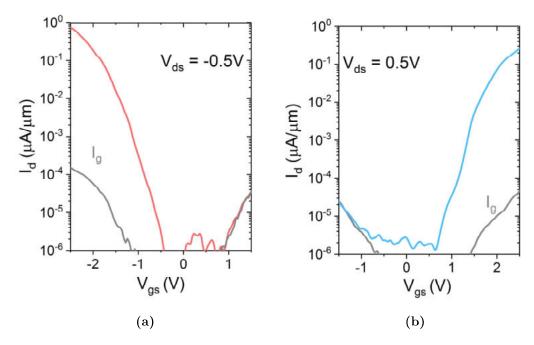

| 3.    | 26 DC transfer characteristics $I_d$ - $V_{gs}$ for (a) p-TFET and (b) n-TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|       | with suppressed ambipolar behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53       |

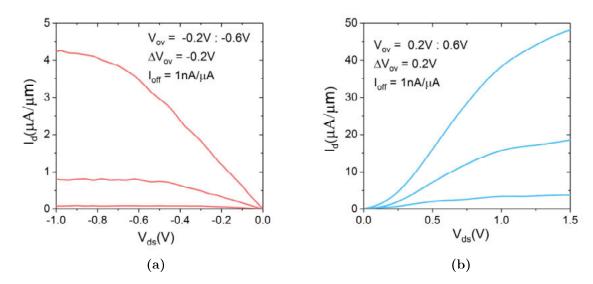

| 3.    | 27 DC output characteristics $I_{d}$ - $V_{ds}$ for both (a)p-TFET and (b)n-TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|       | with suppressed ambipolar behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54       |

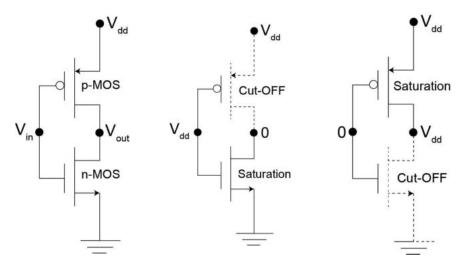

| 4.    | 1. Coherenties of Complementary MOC inventor as well as high input and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| ч.    | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| т.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56       |

|       | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56       |

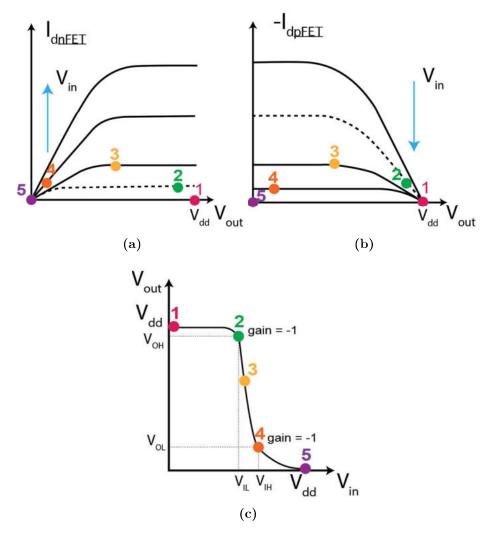

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56       |

|       | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56       |

|       | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56<br>57 |

|       | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

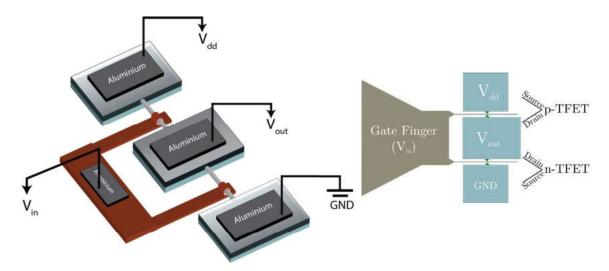

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage.  (a) Inversion of $I_{dp}$ and shifting the x-axis of p-MOS output characteristics. (b) n-MOS output characteristics. (c) Corresponding load-line plot by super imposing n and p-MOS output curves. At each marked point both devices have the same current at a specific $V_{in}$ voltage.  Schematics of single NW sSi GAA CTFET inverter with both transistors on the same mesa. Source and drain of n-TFET and p-TFET                                                                                                                                                                                                  | 57       |

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage.  (a) Inversion of $I_{dp}$ and shifting the x-axis of p-MOS output characteristics. (b) n-MOS output characteristics. (c) Corresponding load-line plot by super imposing n and p-MOS output curves. At each marked point both devices have the same current at a specific $V_{in}$ voltage.  Schematics of single NW sSi GAA CTFET inverter with both transistors on the same mesa. Source and drain of n-TFET and p-TFET and their corresponding bias mode is specified.  Individual transfer characteristics of p-TFET(a) and n-TFET(b) for                                                                              | 57       |

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage.  (a) Inversion of $I_{dp}$ and shifting the x-axis of p-MOS output characteristics. (b) n-MOS output characteristics. (c) Corresponding load-line plot by super imposing n and p-MOS output curves. At each marked point both devices have the same current at a specific $V_{in}$ voltage.  Schematics of single NW sSi GAA CTFET inverter with both transistors on the same mesa. Source and drain of n-TFET and p-TFET and their corresponding bias mode is specified.  Individual transfer characteristics of p-TFET(a) and n-TFET(b) for different $V_{ds}$ fabricated on the same mesa to act as an C-TFET inverter. | 57       |

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57<br>59 |

| 4. 4. | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57       |

| 4.    | low-input circuits. $V_{in}$ is connected to the gate and $V_{dd}$ is the supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57<br>59 |

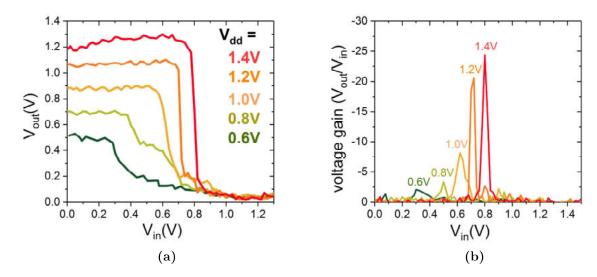

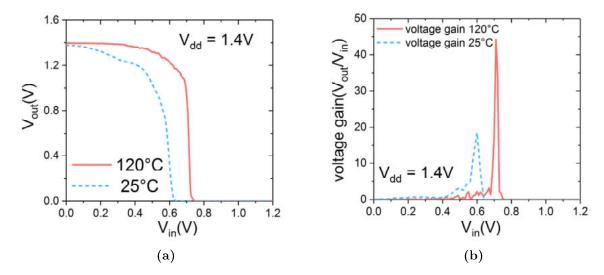

| 4.6  | Room-temperature measurement of single NW GAA c-TFET inverter.  (a) Voltage transfer characteristics(VTC).(b) Corresponding voltage gain of VTC, $dV_{out}/dV_{in}$                                                                                                                                                                                                                                                                                                                                                                            | 62 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

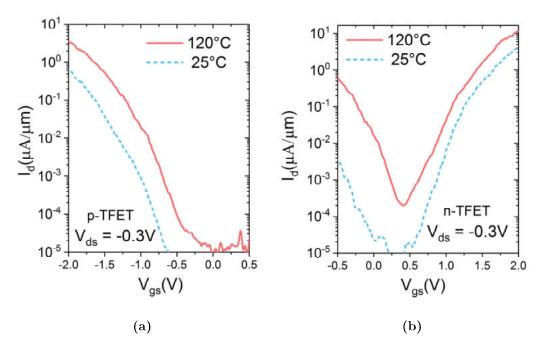

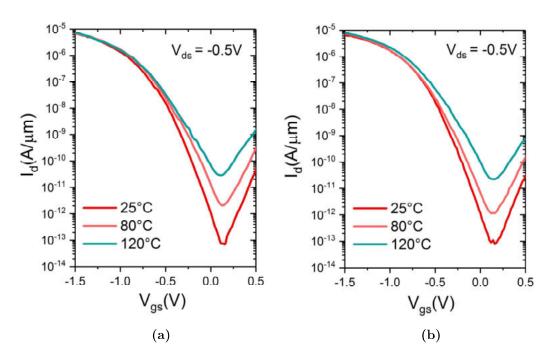

| 4.7  | High temperature measurement of DC transfer characteristics $I_d$ - $V_{gs}$ for both (a)p-TFET and (b)n-TFET devices                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

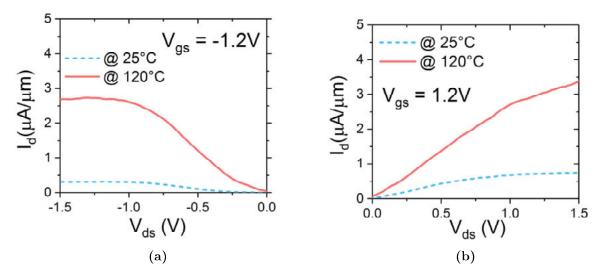

| 4.8  | Output characteristic $I_d$ - $V_{ds}$ for both (a) p-TFET and (b) n-TFET devices at room temperature and $120^{\circ}\text{C}$                                                                                                                                                                                                                                                                                                                                                                                                                | 64 |

| 4.9  | High temperature measurement of a single NW GAA c-TFET inverter at 120°C. (a) Voltage transfer characteristics(VTC).(b) Extracted voltage gain $dV_{out}/dV_{in}$                                                                                                                                                                                                                                                                                                                                                                              | 65 |

| 4.10 | Transfer charactersitics $I_d$ - $V_{gs}$ for (a) p-TFET and (b) n-TFET, with suppressed ambipolarity using gate-drain underlap, integrated on the same mesa for logic inverter measurement, as explained in Figure 4.3.                                                                                                                                                                                                                                                                                                                       | 66 |

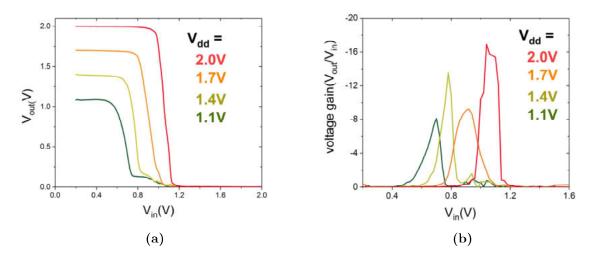

| 4.11 | Single NW GAA C-TFET inverter with suppressed ambipolar behavior. (a) Voltage transfer characteristics.(b) Corresponding voltage gain of VTC                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

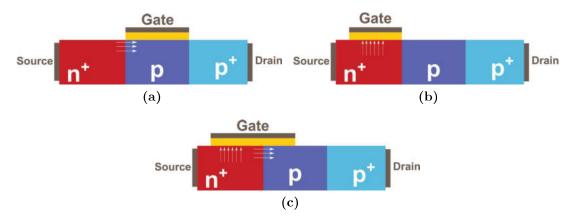

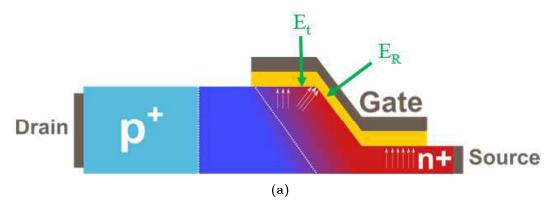

| 5.1  | pTFET device configuration. (a) Tunneling path of carriers in case of point-tunneling, where tunneling occurs at the source channel interface. (b) Tunneling path of carriers in case of line-tunneling where the tunneling takes place in the gate/source overlapped region with a direction parallel to the gate electrical field. By applying a gate voltage a depletion/inversion region beneath the gate is formed and carriers tunnel to the oxide interface. (c) In a real device, both tunneling mechanisms contribute to the current. | 69 |

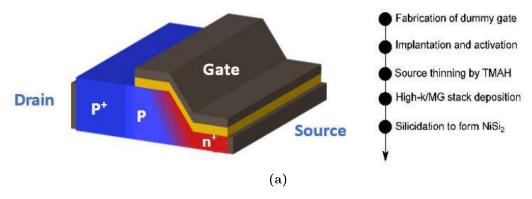

| 5.2  | Device schematics and key fabrication process steps. After implantation and activation, the source is thinned down through wet etching to get rid of EOR damages                                                                                                                                                                                                                                                                                                                                                                               | 70 |

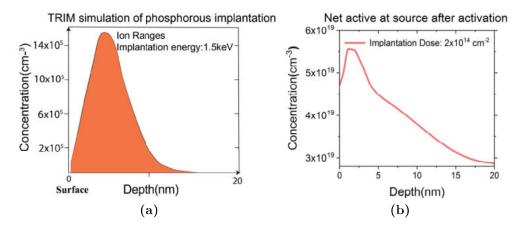

| 5.3  | (a) TRIM simulation of the implantation. Point of maximum damage and EOR region are marked in the plot. (b) Net active dopant concentration achieved using Sentaurus TCAD process simulation for                                                                                                                                                                                                                                                                                                                                               |    |

|      | implantation and subsequent spike annealing at 1050°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71 |

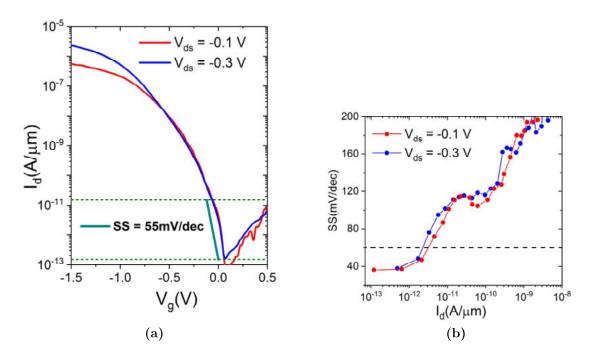

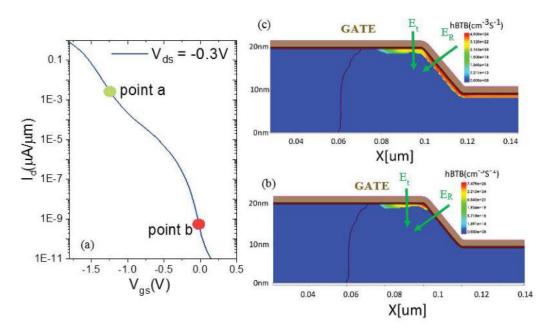

| 5.4  | (a) DC Transfer characteristics $I_d$ - $V_{gs}$ of transistor T1 pTFET with                                                                     |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | lower source doping. (b) SS vs $I_d$ plot of the transfer curve. The                                                                             |    |

|      | hump is caused by the different line-tunneling onset voltages in the                                                                             |    |

|      | top corner and in the thin source area                                                                                                           | 73 |

| 5.5  | Different tunneling mechanisms in the fabricated device are shown                                                                                |    |

|      | schematically. Line tunneling takes places in two distinct regions: one                                                                          |    |

|      | in the thin source area and the other on the surface of the thick part                                                                           |    |

|      | of the source. Since the top corner at thick part has a higher electric                                                                          |    |

|      | field due to the existing fringing fields, the tunneling is induced earlier                                                                      |    |

|      | at that point before extending over the ramp and in the end on the                                                                               | _  |

|      | thin part of the source                                                                                                                          | 74 |

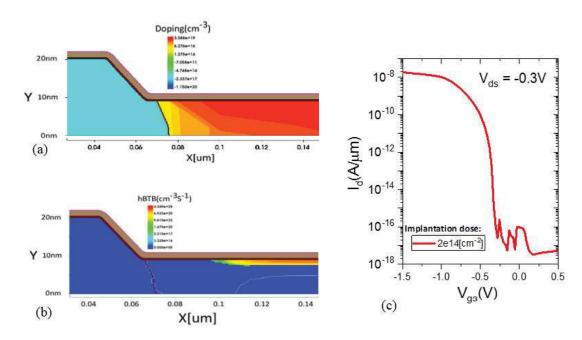

| 5.6  | (a) Simulated transfer characteristics of the fabricated device at $V_{ds}$                                                                      |    |

|      | = -0.3V. (b), (c) show zoomed in contour of the device for different                                                                             |    |

|      | $V_{gs}$ . Source is on the right side, while drain is on the left and gate                                                                      |    |

|      | extends all over the top section of the device. (b) Contour of BTB                                                                               |    |

|      | hole generation at $V_{gs} = -0.1$ V shows that line-tunneling first occurs at the corner due to the high fringing field. (c) BTBT generation of |    |

|      | carriers at $V_{gs}$ = -1V shows that the hump in the characteristics is due                                                                     |    |

|      | to the late start of line-tunneling in the thinner area of source                                                                                | 75 |

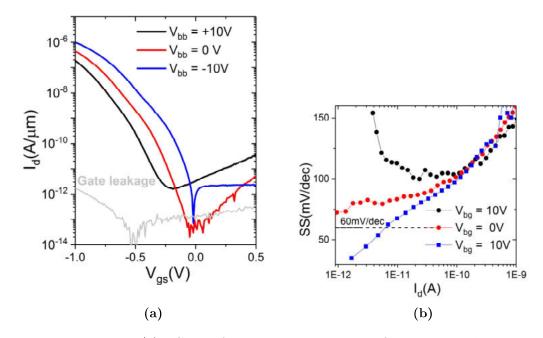

| 5.7  | (a) Measured transfer characteristics of a pTFET device with higher                                                                              | 10 |

| 0.1  | source doping. Notice the obvious shoulder in the curve, which is                                                                                |    |

|      | caused by stronger fringing field and starts earlier than line-tunneling                                                                         |    |

|      | at the thin part. (b) SS vs Id plot shows the effect of the bump more                                                                            |    |

|      | clearly.                                                                                                                                         | 76 |

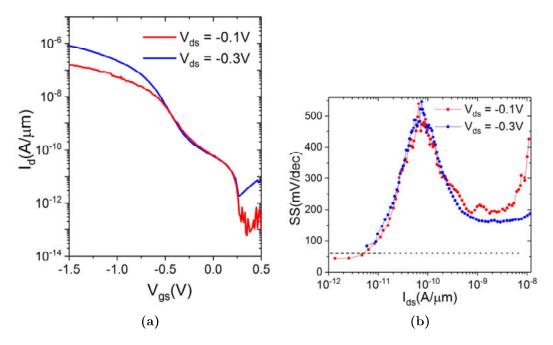

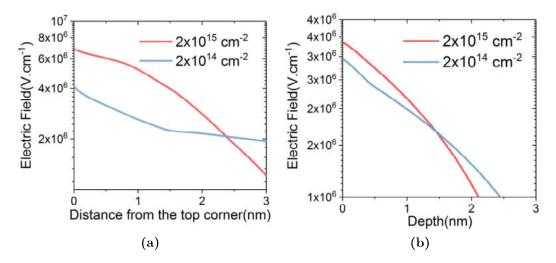

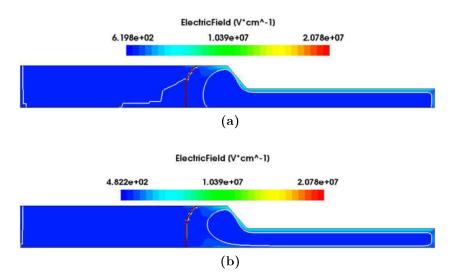

| 5.8  | Simulated electric field in the device for two different implantation                                                                            |    |

|      | doses. (a) In the diagonal direction from the top corner. (b) Normal                                                                             |    |

|      | to the thin part of the source surface                                                                                                           | 77 |

| 5.9  | DC output characteristics $I_d$ - $V_{ds}$ of device T1 showing very good satu-                                                                  |    |

|      | ration and slightly super-linear behavior at small drain-source voltages.                                                                        | 77 |

| 5.10 | The proposed device structure with the doping only in the thin area                                                                              |    |

|      | (a). (b) simulated BTB hole generation. In contrast to the previous                                                                              |    |

|      | device doping, now BTBT only takes place under the gate on the thin                                                                              |    |

|      | area of source. (c) Simulated transfer characteristics with improved                                                                             |    |

|      | subthreshold slope.                                                                                                                              | 78 |

| 5.12 | Simulated depletion regions for different back gate bias voltages (a) $V_{bg} = 0$ (b) $V_{bg} = -10$ . The color range shows the electric field in the device while depletion layer is marked by the white lines. Increasing the absolute value of back gate bias extends depletion region at source and drain sides           | 80 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.13 | Extracted output conductance $g_d$ from the output characteristics of device T1. $g_d$ rapidly decreases to small values, indicating good current saturation.                                                                                                                                                                   | 80 |

| 5.14 | Extracted transconductance $g_m$ and transconductance efficiency $g_m/I_d$ for device T1. As indicated in the plot, for small currents, transconductance efficiency goes beyond values achievable by MOSFETs. Due to small $g_m$ , this device is suitable for low-frequency applications                                       | 81 |

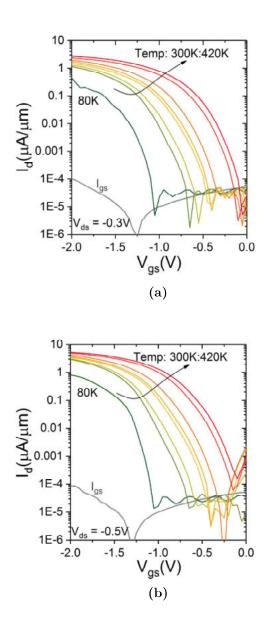

| 5.15 | Measured transfer characteristics $I_d$ - $V_{gs}$ for the planar line-tunneling Field at different temperatures for $V_{ds}=$ -0.3V and $V_{ds}=$ -0.5V                                                                                                                                                                        | 82 |

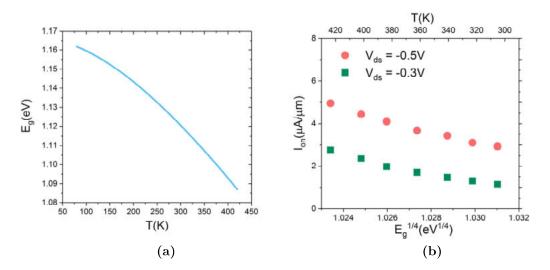

| 5.16 | (a) $E_g$ vs T temperature plot for silicon (b) $I_{on}$ versus $E_g 1/4$ showing a linear trend with small deviation as an indication of line tunneling aligned with the gate electric field at the thin part of the source of transistor                                                                                      | 83 |

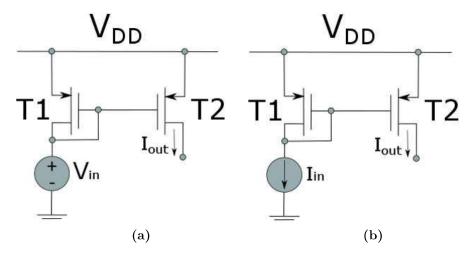

| 6.1  | Biasing scheme of the current mirror. (a) Current amplifier. (b) Current bias                                                                                                                                                                                                                                                   | 86 |

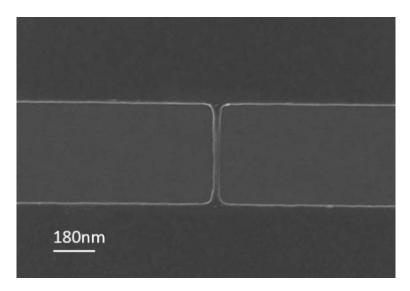

| 6.2  | scanning electron microscopy(SEM) image of a nanowire 400nm long and 35nm wide                                                                                                                                                                                                                                                  | 87 |

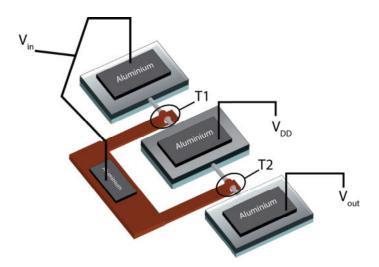

| 6.3  | 3D schematic of the fabricated current mirror circuit with biasing voltage layout                                                                                                                                                                                                                                               | 87 |

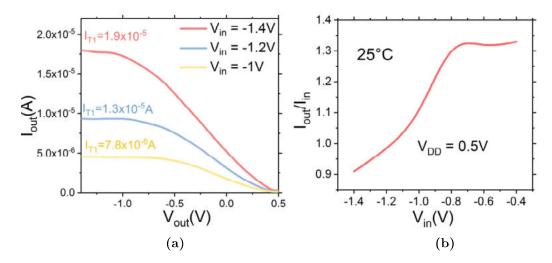

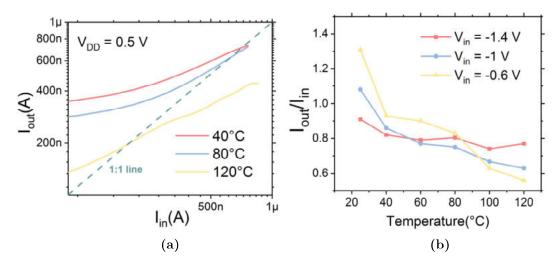

| 6.4  | (a) $I_{out}$ current versus $V_{out}$ voltage at different $V_{in}$ voltages based on biasing scheme in Figure 6.1(a) showing good saturation and match between transistors. (b) Mirror ratio $I_{out}/I_{in}$ is plotted vs $V_{in}$ as a figure of merit for the current amplifier biasing scheme at a fixed $V_{DD}$ = 0.5V | 88 |

## LIST OF FIGURES

| 6.5 | (a) Measured $I_{out}$ of the current mirror by changing $I_{in}$ for biasing               |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | scheme in Figure 6.1(b). The plot reveals reduction of $I_{out}$ for increas-               |    |

|     | ing T at constant $I_{in}$ . (b) Mirror ratio $I_{out}/I_{in}$ for three different $V_{in}$ |    |

|     | voltages based on biasing scheme of Figure 6.1(a). The $I_{T1}$ at 25°C is                  |    |

|     | also written for each plot                                                                  | 89 |

| 6.6 | Transfer characteristics $I_d$ - $V_{gs}$ for each device measured from 25°C to             |    |

|     | 120°C. (a) T1 transistor (b) T2 transistor                                                  | 90 |

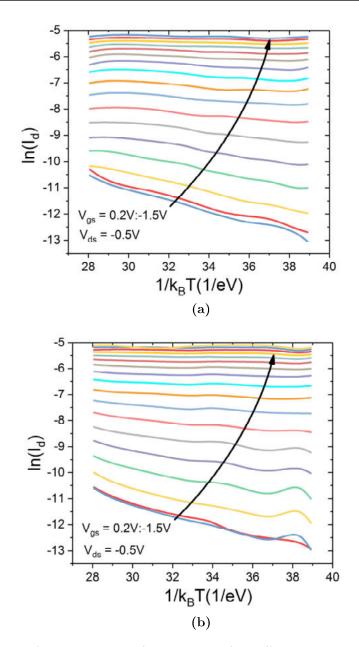

| 6.7 | Arrhenius plot of T1 and T2 for different $V_{gs}$ voltages from 0.2V to                    |    |

|     | -1.5V at $V_{ds} = -0.5$ V. The slope of each line represents the activa-                   |    |

|     | tion energy Ea, which basically shows the sensitivity of the current to                     |    |

|     | temperature changes at a specific voltage                                                   | 91 |

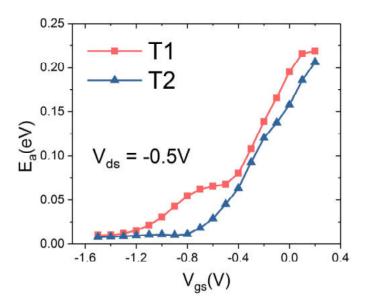

| 6.8 | Activation energy Ea plot for both transistors T1 and T2 of the current                     |    |

|     | mirror as a function of gate voltage $V_{gs}$ . The plot shows higher sensi-                |    |

|     | tivity of T1 transistor current to temperature with respect to transistor                   |    |

|     | To                                                                                          | 02 |

# Chapter 1

# Introduction

According to CISCO's Global Cloud Index(GCI), by 2020 there will be more people with mobile phones than people who have access to conventional electricity distribution at home. Moreover, large scale use of sensors for internet of things(IOT) applications is booming and finding new applications in industry[1]. When billions of sensors are used, their size and power efficiency will be the most important issues [2]. Up to now, the semiconductor industry has managed to follow the Moore's law over 50 years by employing innovative designs like multi-gate transistors [3] or developing high-k dielectrics[4], and scaling down the technology node. Using high resolution deep ultraviolet light lithography techniques coupled with a gate-all-around device architecture, IBM fabricated 5nm silicon chips in 2017. Samsung plans to produce 4nm node chips by 2020. However, it may not be possible to continue this trend as leakage currents due to extreme physical limits will keep increasing[5]. Even though there has been immense technology leaps, Moore's law is slowing down, for example by 2013 Intel had already slowed down launching new technology nodes. As our society immensely relies on faster devices with lower power consumption, there is a need for new device concepts beyond the Moore's era.

As gate length of devices is reduced and number of transistors in an integrated circuit increases, the power dissipation caused by static and dynamic power consumption of the chips also increases dramatically. This is caused by the inherent physical limitation of MOSFET current in subthreshold region that can be increased with respect to gate voltage ideally with a rate of 60mV/dec at room temperature. The implication of this limit for power dissipation is two fold. Firstly, by decreasing  $V_{th}$  to scale  $\text{down}V_{DD}$ ,  $I_{off}$  due to the 60mV/dec limit increases exponentially, causing static power consumption to rise. On the other hand, dynamic power consumption is dependent on the square of voltage bias, and thus by keeping the  $V_{th}$  constant and directly decreasing  $V_{DD}$ , dynamic power consumption can be greatly decreased. On

the other hand, this also hinders the switching frequency of the device, which is not desirable. New device concepts to achieve SS less than 60mV/dec are required to tackle this problem. Different field controlled switching mechanisms like mechanical switches[6, 7], impact ionization[8, 9], ferroelectricity[10] and band to band tunneling(BTBT)[11] can fulfill the SS requirement. In the current work we will focus on BTBT switching in tunneling field effect transistor(TFET) since it does not have limited switching speed associated with the other aforementioned mechanisms[12].

The earliest observation of band to band tunneling dates back to 1952 when Stuetze[13] recorded the ambipolar nature of a gated Ge p-n diode. Following that, in 1958 Esaki[14] discovered p-n interband tunneling. Over the years different TFET concepts were developed but it was not until 2004 when Appenzeller[15], Wang[16] and Bhuwalka[17] reported sub 60mV/dec switching in a TFET. Since then TFETs based on different materials like Si[18, 19, 20],Ge[21] and III-V materials[22] have shown sub 60mV/dec behavior, yet the average subthreshold slope for these devices is well above 60mV/dec and they also exhibit either low  $I_{on}$  current or low  $I_{on}/I_{off}$  ratio. Among different materials, silicon based TFETs attract a lot of interest due to their compatibility with the conventional CMOS fabrication process and better material quality which helps to keep the costs low and makes it feasible to achieve complementary TFET circuits[23, 24].

Within the framework of this thesis, two different design concepts of TFETs will be evaluated. First, highly scaled silicon single nanowire TFETs with superior electrostatics and optimized doping processes for both n- and p- TFETs which are investigated for low-power analogue and digital circuit applications. Secondly, planar silicon TFETs with a novel approach to reduces trap assisted tunneling and exploit sharper switching of line tunneling are fabricated and also simulated by use of TCAD technology.

The content of this thesis is divided into five chapters. Following this introduction, the basic motivation, theory and concepts which are required to understand underlying physics are discussed in Chapter 2. Design considerations and non-ideal processes which limit performance of TFETs are specifically explained. Chapter 3 presents the experimental results of silicon single GAA nanowire TFETs and the course of carefully optimizing key-process parameters to achieve maximum  $I_{on}$  and minimum average subthreshold slope. In addition, analogue figures of merit, low temperature measurements and density of interface trap are also discussed. Last but not least,

systematic suppression of ambipolar behavior is also investigated. Next, chapter 4 presents the experimental results of fabricated complementary TFET logic inverter circuits. The TFET circuits have been fabricated with and without ambipolarity to compare the results. Moreover, high-temperature behavior of the inverter is also characterized. In Chapter 5 fabrication of a novel structure for taking advantage of line-tunneling in silicon TFETs is presented with experimental electrical characterization. It is shown that these devices can achieve average SS of 55mV/dec for low currents. Using TCAD simulation, the device working principles are inferred and explained in detail. Finally, in Chapter 6 results for experimental demonstration of a two-TFET current mirror are presented. It is shown that this circuit may operate stable even at elevated temperatures.

# Chapter 2

# Theoretical Background

This chapter begins by introducing the limitation of power supply scaling in conventional MOSFET technology and explaining how it motivates development of novel device structures like TFETs. Moreover, the working principle of MOSFET and TFET is, from physics point of view, discussed and compared. Subsequently, various design aspects as well as different non-idealities that pose significant challenges to TFET operation are explained.

#### 2.1 Limitations of power scaling in ICs

In order to gain a deeper understanding how MOSFET inherently limits the supply voltage  $V_{DD}$  scaling at a given technology node, one should consider the power dissipation of its operation. It comprises of two distinct terms, namely dynamic and static power consumption, related to  $V_{DD}$ . It can be written as:

$$P_{Total} = P_{Dynamic} + P_{Static} = C_T \cdot V_{DD}^2 \cdot f + V_{DD} \cdot I_{off}$$

(2.1)

where  $C_T$  is the total capacitance when transistor switches, f is the switching frequency,  $I_{off}$  is the off-state leakage current.

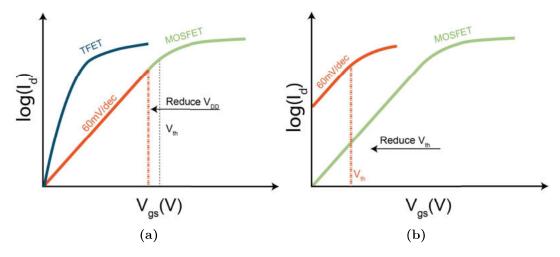

Looking at this equation, it makes sense to decrease  $V_{DD}$  in order to scale down power dissipation. To achieve this goal, there are two options available: firstly to function in the subthreshold region by decreasing  $V_{DD}$  and keeping threshold voltage  $V_{th}$  unchanged (Figure 2.1(a)). This is not an ideal case because the operation frequency subsequently decreases.

The other measure to take is to scale down threshold voltage  $V_{th}$  in order to keep the on current high by lowering  $V_{DD}$ . This method, however, does not maintain a proper  $I_{on}/I_{off}$  ratio. To understand this issue one should understand the concept of inverse subthreshold swing, abbreviated as SS. It basically quantifies the required voltage to increase current for an order of magnitude. This value for a MOSFET is physically limited to 60mV/dec at room temperature due to thermionic processes. Therefore, decreasing  $V_{th}$  is like shifting the whole  $\log(I_d)$ - $V_{gs}$  curve to the left, hence increasing off-current exponentially, leading to much higher static power consumption (Figure 2.1(b)).

Considering this discussion, a novel device concept, like TFETs, is needed to overcome the 60mV/dec limit of MOSFETs as shown in Figure 2.1(a).

**Figure 2.1:** (a) Scaling down  $V_{DD}$ . In comparison the characteristics of a TFET is also depicted (b) Decreasing  $V_{th}$  to reach desired on current at a lower  $V_{DD}$ , resulting in high  $I_{off}$ .

## 2.2 MOSFET operation

Generally, field effect transistors (FETs) are semiconductor devices with two ohmic contacts, called drain and source, where charge transport between the two is controlled via a third one called the gate contact. The gate-channel structure is a metal-oxide-semiconductor (MOS) where the gate is separated by an insulating dielectric layer from the channel. An inversion layer beneath the oxide would act as a conducting channel where the carriers in case of a p-type substrate are electrons and in case of an n-type substrate are holes. The former case is called an n-MOSFET where the

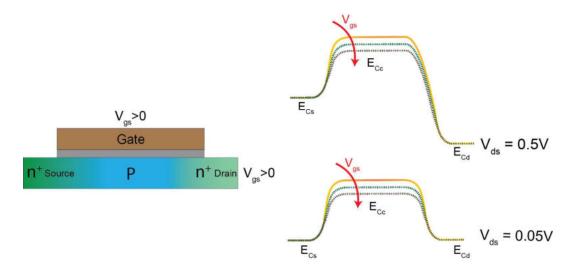

latter is a p-MOSFET. Figure 2.2 shows the schematics and energy band diagram for an n-MOSFET at low and high  $V_{ds}$  voltages.

Figure 2.2: Schematic illustration of an n-MOSFET and its energy band diagram. By increasing the applied gate voltage  $V_{gs}$ , potential barrier height for electrons decreases allowing thermionic transport from the source to drain.

By moving the channel bands down, the thermally excited electrons can transmit from source to drain. To understand the physical limit of 60mV/dec for SS at room temperature, Landauer formalism can be used for the 1D case to evaluate the subthreshold behavior of MOSFET as follows:

$$I_d = \int_{-\infty}^{\infty} \frac{2e}{h} T(E)(f_s(E) - f_d(E)) dE$$

(2.2)

where  $f_s$  and  $f_d$  are the Fermi distribution in source and drain, e is the elementary charge and h is the Planck constant. T(E) is the transmission probability from the potential barrier. For simplicity we let T(E) = 1 for energies higher than  $E > \phi_f^0$  and otherwise T(E) = 0.  $\phi_f^0$  denotes the conduction band energy of channel which is the potential barrier height for electrons. Therefore one can rewrite the relationship as:

$$I_d = \int_{\phi_f^0}^{\infty} \frac{2e}{h} (f_s(E) - f_d(E)) dE$$

(2.3)

#### 2. Theoretical Background

Since in the subthreshold region  $\phi_f^0$  is much larger than the chemical potential of source  $\mu_s$  and drain  $\mu_d$ ,  $f_s$  and  $f_d$  can be approximated by the Boltzmann distribution. Moreover, considering small  $V_{ds}$  voltage, then  $f_s \gg f_d$  and one can approximate the previous equation as:

$$I_{d} = \int_{\phi_{f}^{0}}^{\infty} \frac{2e}{h} \exp\left\{\frac{\mu_{s} - E}{k_{B}T}\right\} dE = \frac{2e}{h} k_{B}T \exp\left\{\frac{\mu_{s} - \phi_{f}^{0}}{k_{B}T}\right\}$$

(2.4)

In order to calculate inverse subthreshold slope, we must rewrite  $I_d$  as a function of gate voltage  $V_g$ . The potential barrier height for carriers  $\phi_f^0$  is dependent on the gate voltage through a capacitive voltage divider between gate oxide  $C_{ox}$ , interface capacitance  $C_{it}$  and depletion capacitance  $C_{dep}$ :

$$\frac{\partial \phi_f^0}{\partial V_a} = e \frac{C_{ox}}{C_{ox} + C_{it} + C_{dep}} \tag{2.5}$$

by inserting 2.5 into 2.4 inverse subtreshold slope SS can be calculated as follows:

$$SS = \left[\frac{\partial log I_D}{\partial V_q}\right]^{-1} = ln(10)\frac{k_B T}{e} \left(1 + \frac{C_{dep} + C_{it}}{C_{ox}}\right)$$

(2.6)

If the oxide capacitance is sufficiently large to reach the quantum capacitance limit ( $C_{dep} + C_{it} < C_{ox}$ ), then at room temperature T = 300K equ. 2.7 yields:

$$SS = ln(10)\frac{k_B T}{e} \approx 60mV/dec$$

(2.7)

Therefore an ideal MOSFET in 1D structure with quantum capacitance limit will need a minimum of 60mV of gate voltage at room temperature to increase drain current by an order of magnitude.

# 2.3 Tunnel FET operation

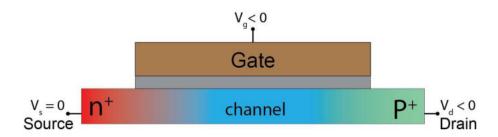

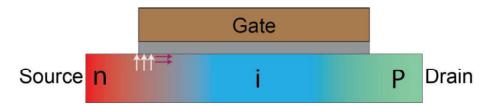

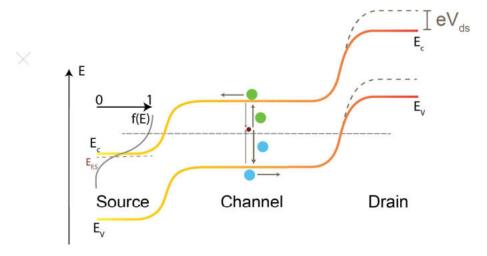

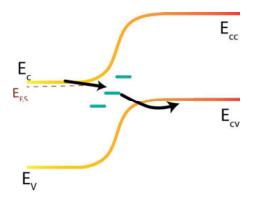

A promising candidate to replace MOSFET in next generation low-power digital and analogue circuits is tunnel field effect transistor(TFET). It is basically a reversed biased and gated p-i-n diode as shown in Figure 2.3. The oppositely doped source and drain yields a staircase-like energy band structure for a TFET as shown in Figure 2.4. Depending on how the device is biased it may either function as an nTFET or a pTFET.

**Figure 2.3:** Schematic illustration of a TFET structure. It is a gated pin diode which is reversely biased through the gate on top of the gate oxide.

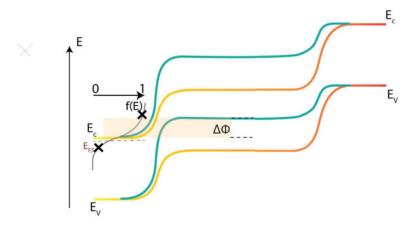

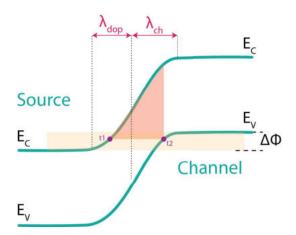

Here we assume a negative voltage  $V_d$  is applied on the p<sup>+</sup> doped junction and the n<sup>+</sup> doped junction is connected to the ground (Figure 2.3). As shown in Figure 2.4, firstly the device is in equilibrium and does not conduct current. By applying a negative voltage to the gate  $V_{gs} < 0$ , the energy bands in channel move up, and as soon as the valence band of channel  $E_{CV}$  moves above the conduction band of source  $E_{CS}$  an energy overlap window appears that allows carriers to tunnel from the source conduction band to the channel valence band, the distance of which, depends on the band-bending sharpness at the source-channel junction. This process is the so-called band to band tunneling (BTBT). In Figure 2.4 the energy overlap is marked as  $\Delta\Phi$ . Since tunneling of carriers outside of the energy overlap  $\Delta\Phi$  is blocked, BTBT acts as a band-pass filter, filtering out the high and low parts of the Fermi distribution leading to smaller SS than 60 mV/dec and less temperature susceptibility.

#### 2.3.1 BTBT model

The band bending overlap at the source-channel junction of a TFET can be approximated as a triangular barrier as shown in Figure 2.5. Therefore, the tunneling probability T may be calculated using Wentzel-Kramers-Brillouin(WKB) approximation[25]:

$$T_{WKB} = -2 \exp\left\{ \int_{t_1}^{t_2} |k(t)| dt \right\}$$

(2.8)

where  $t_1$  to  $t_2$  is the tunneling path and k(t) is the wave vector of the carriers which for an electron with energy E in the conduction band  $E_C$  is given by:

**Figure 2.4:** Illustration of TFET band structure when biased as a p-TFET. By increasing the absolute value of gate voltage  $V_g$  the channel bands move up until an energy overlap for BTBT between channel valance band and source conduction band appear.

$$k(t) = \sqrt{\frac{2m^*}{\hbar^2}(E - E_C)} = \sqrt{\frac{2m^*}{\hbar^2}(-e\xi t)}$$

(2.9)

Taking the integral after inserting 2.9 in 2.8 provides:

$$T_{WKB} = \exp\left\{-\frac{4\sqrt{2m^* E_g^{1.5}}}{3\hbar(e\xi)}\right\}$$

(2.10)

where  $\xi$  is the electric field being dependent on the band bending abruptness, which itself is a sum of doping and electrostatic screening lengths. Hence  $\xi$  can be approximated as  $(E_g + \Delta \phi)/(\lambda_{ch} + \lambda_{dop})$ , yielding from equ. 2.10:

$$T_{WKB} = \exp\left\{-\frac{4(\lambda_{dop} + \lambda_{ch})\sqrt{2m^*E_g^{1.5}}}{3\hbar(\Delta\phi + E_g)}\right\}$$

(2.11)

According to equ. 2.11 to achieve an optimum tunneling probability small  $E_g$ , small effective mass  $m^*$ , good electrostatics and sharp doping profile are needed.